CMOS Logic Gate - GeeksforGeeks

2024年6月6日 · AOI (and-or-invert) and OAI (or-and-invert) gates are two basic configurations that can be realized using CMOS logic. The CMOS realization of these two types of gates is shown below. Note that the two gates are dual to each other.

CMOS - Wikipedia

CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips (including CMOS BIOS), and other digital logic circuits.

CMOS Logic Gates Explained - ALL ABOUT ELECTRONICS

2023年4月14日 · In this article, CMOS Logic is explained, and how to design different logic gates using CMOS Logic is explained in detail.

What is a CMOS : Working Principle & Its Applications - ElProCus

In CMOS technology, both N-type and P-type transistors are used to design logic functions. The same signal which turns ON a transistor of one type is used to turn OFF a transistor of the other type. This characteristic allows the design of logic devices using only simple switches, without the need for a pull-up resistor.

Starting wafer is pure silicon crystal. Multiple process steps deposit new materials and etch existing layers using photolithography (light focused through masks). Modern logic chips fabricated on 20cm (8”) wafers, ~100s chips/wafer. Wafer …

CMOS Logic Gate in Digital Electronics - Online Tutorials Library

CMOS technology employs both NMOS (N-Channel Metal Oxide Semiconductor) and PMOS (P-Channel Metal Oxide Semiconductor) logic to implement different types of digital functions. CMOS technology is widely being used in realizing digital logic gates due to its key advantages, such as fast switching speed, low power consumption, high voltage range ...

Basic CMOS Logic Gates - Technical Articles - EE Power

2021年10月27日 · Learn about gates built with the CMOS digital-logic family. Logic gates that are the basic building block of digital systems are created by combining a number of n- and p-channel transistors. The most fundamental connections are the NOT gate, the two-input NAND gate, and the two-input NOR gate.

MOS Transistors, CMOS Logic Circuits. Remember the resistor? But it has 3 terminals! No current flows into the gate terminal! • This really simple model is suitable for applications where there’s one value of “On” voltage. How Does an nMOS Transistor Actually Work? Oops ... • Similar to nMOS, but upside down!

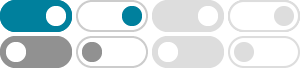

For every CMOS device, there are essentially two separate circuits: 1) The Pull-Up Network 2) The Pull-Down Network The basic CMOS structure is: A CMOS logic gate must be in one of two states! V DD A B C D A B C D PUN PDN Inputs Output Y=f A,B,C,D()

2018年9月11日 · What is the difference between the two circuits? How do voltage levels at the output of this gate differ from that of the pass-transistor multiplexer in the previous foil? How many transistors are needed? If not then it takes 6 transistors... Questions?

- 某些结果已被删除